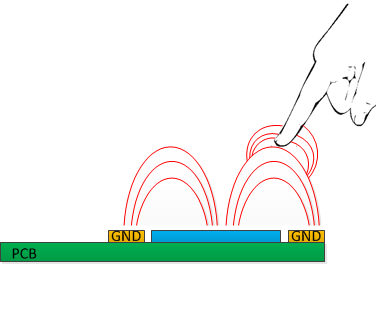

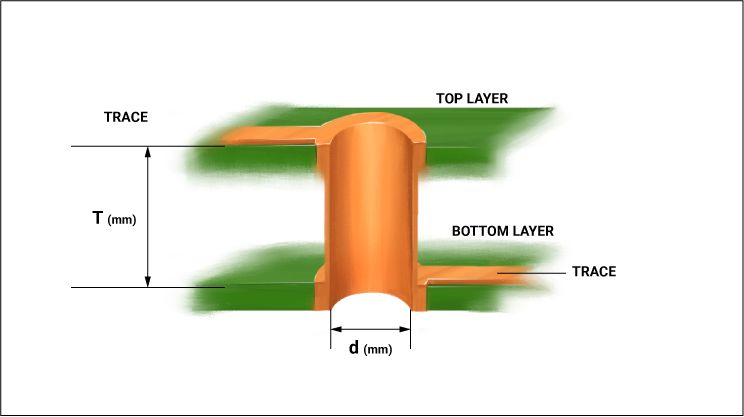

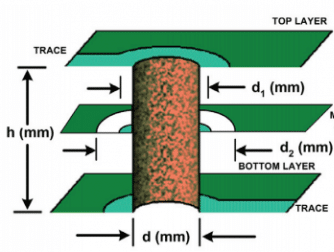

Model of IC package and PCB parasitic (C P IN ) is assumed to have a... | Download Scientific Diagram

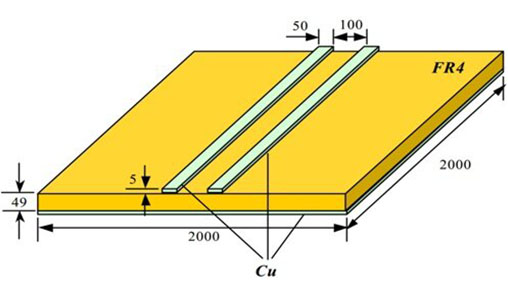

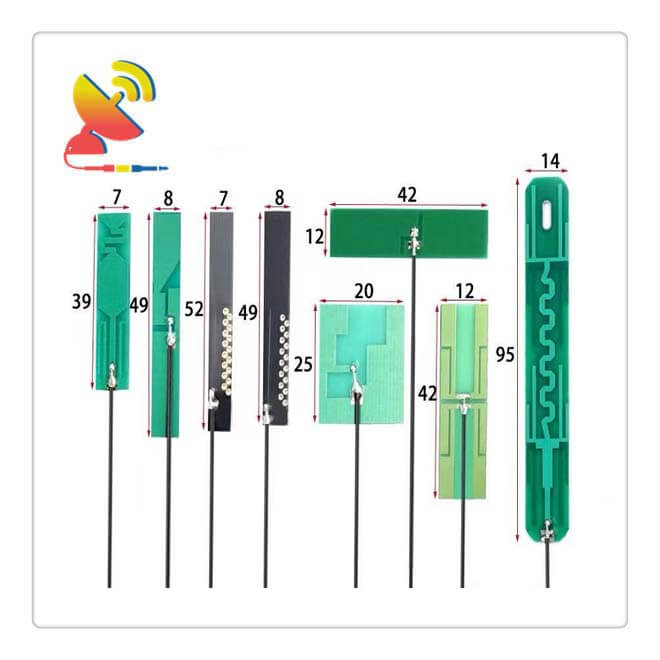

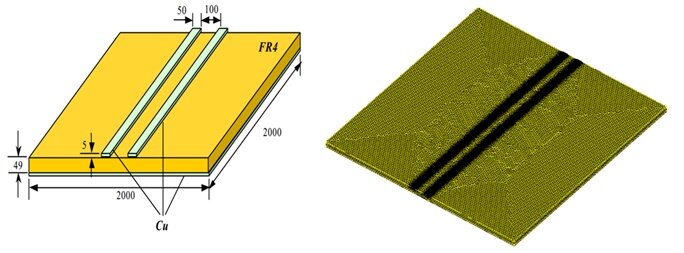

Geometrical parameters of a square-shaped PCB inductor. (a) Top view of... | Download Scientific Diagram

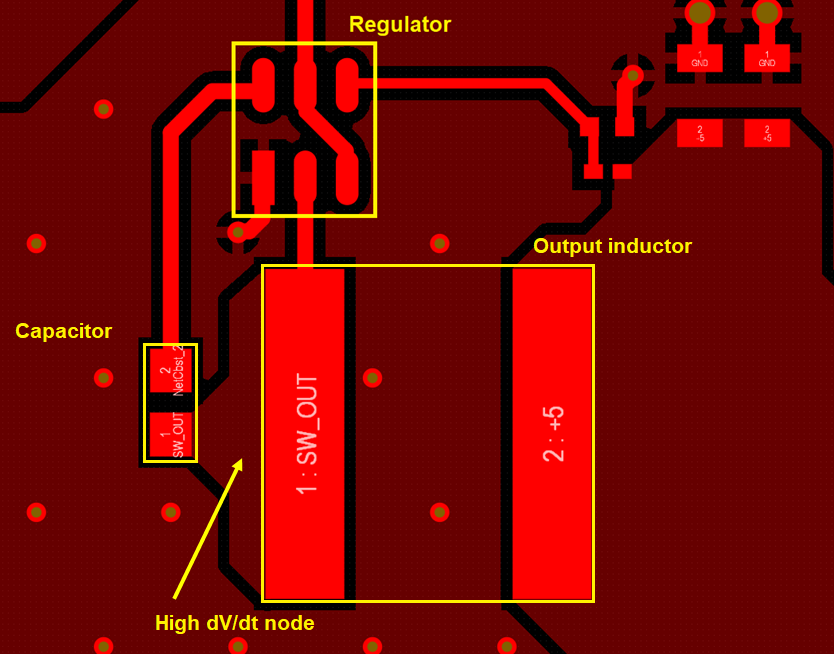

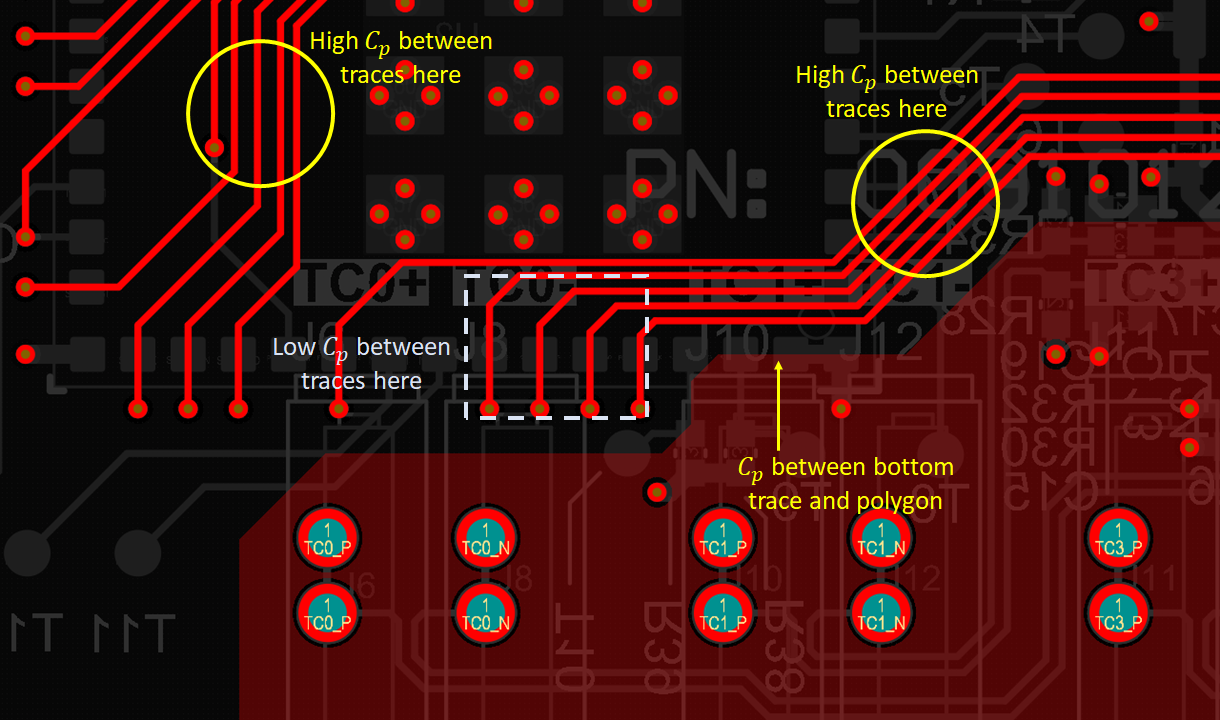

Parasitic Capacitance Eqoss Loss Mechanism, Calculation, and Measurement in Hard-Switching for GaN HEMTs

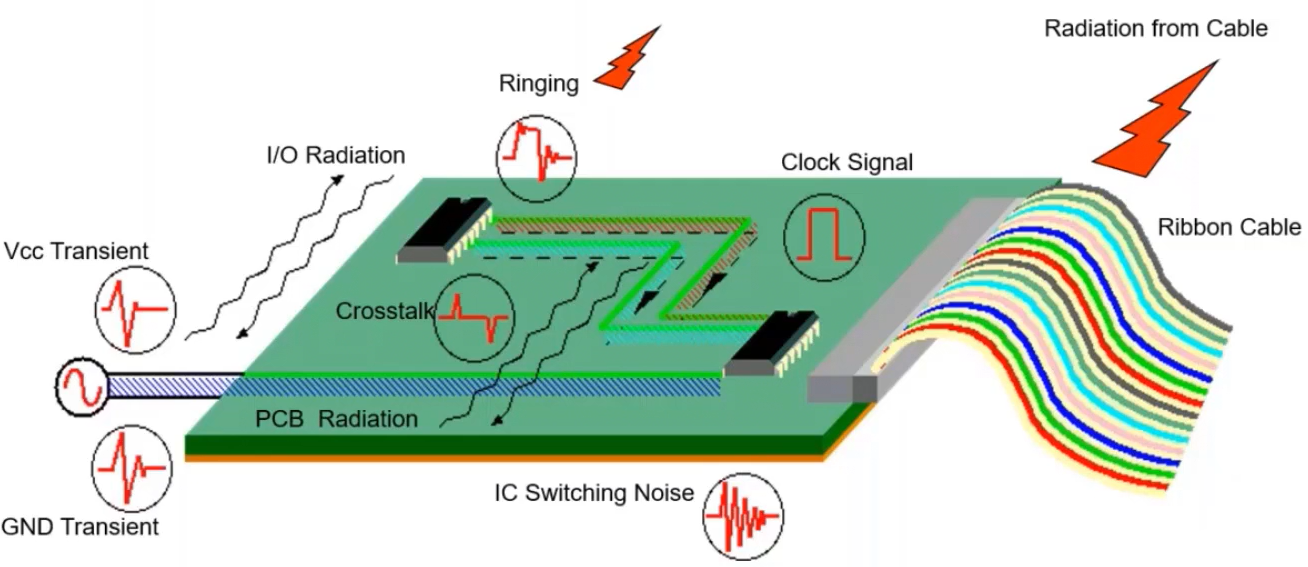

SI/PI degradation due to package-common-mode resonance caused by parasitic capacitance between package and PCB | Semantic Scholar